これ

技術革新サイトの編集者 – 2022 年 8 月 12 日

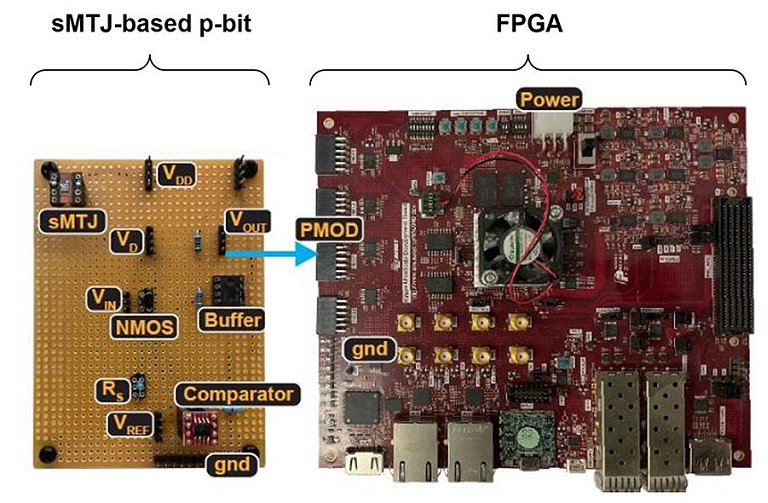

標準の FPGA チップに挿入された確率的スピントロニクス ビットで構築された異種のポスト コンピューター プロトタイプ。

[Imagem: Kerem Camsari et al. (2022)]

p-コンピューター

米国、イタリア、日本のチームが、ムーアの法則の崩壊を克服するための大きな期待の 1 つである、p コンピューターとしても知られる確率的コンピューターの実用的なバージョンの構築に初めて成功しました。

コンピューターは、その縮小版です。 確率プロセッサ 同じチームが 2019 年に発表したものです。

p-computer は、確率的ビット (p-bits) と呼ばれる自然にランダムなビルディング ブロックを使用します。 従来のコンピューター ビットとは異なり、p ビットは特定の値を持たず、値の間で変動します。

量子コンピューターが本質的に量子の問題を解決しようとするのと同じように、p コンピューターは、人工知能や機械学習で広く使用されている確率的アルゴリズムを処理しようとします。 しかし、確率的コンピューターは室温で動作し、従来のハードウェアで作られています。

確率プロセッサ

チームは以前、「確率的磁気トンネル接合」(sMTJ: 確率的磁気トンネル接合)、ただし小規模のみ。

今日達成されたスケーリングは、それ以降に行われた 2 つの進歩に基づいています。

1つ目は、チームがスピントロニクスpビットを従来の半導体集積回路、より具体的には準備ができたらプログラム可能な集積回路であるFPGAに組み合わせることができたことです。 「sMTJ + FPGA」の組み合わせにより、以前の小規模なデモンストレーションを超えて、はるかに大きな p ビット ネットワークをハードウェアに実装することが可能になりました。

次に、量子アルゴリズムの確率的エミュレーションである量子アニーリング シミュレーション (SQA) が、複雑な組み合わせ最適化問題を解決できる異種ポストプロセッサによって実行されました。 このシミュレーションは、 確率的コンピューティングは、量子コンピューティングへのゲートウェイを表します🇧🇷

サンプルレートと消費電力の関数としてのプロセッサー (P1 と P2) の確率的比較 – N1-N4 としてプロットされた GPU。 TPU は G1-G2 としてプロットされ、シミュレートされた量子プロセッサは F1 としてプロットされます。

[Imagem: Kerem Camsari et al. (2022)]

比較

新しいハードウェアをテストするために、チームは、CPU、GPU、TPU などの従来の CPU に対してプロセッサの確率的テストを実行しました (テンソル処理ユニットAIタスクに特化したプロセッサ)、確率的プロセッサは「従来の技術と比較してパフォーマンスと消費電力の大幅な改善を達成できる」と結論付けています。

しかし、ポストコンピュータが市販の代替品になる前に、まだやるべきことがあります.

「現在、’s-MTJ+FPGA’ p-computer は、ディスクリート コンポーネントを使用したプロトタイプです」と、東北大学の深見俊介教授は認めています。 「将来的には、半導体プロセスと互換性のある磁気抵抗ランダム アクセス メモリ (MRAM) テクノロジを使用する組み込みポストコンピュータが可能になるかもしれませんが、これには、材料、物理学、回路設計、およびアルゴリズムの専門家による共同設計アプローチが必要になります。一緒。”

論文: MTJ拡張pビットを使用したシミュレートされた量子アニーリングの実験的評価

著者: Andrea Grimaldi, Kemal Selcuk, Navid Anjum Aadit, Keito Kobayashi, Qixuan Cao, Shuvro Chowdhury, Giovanni Finocchio, Shun Kanai, Hideo Ohno, Shunsuke Fukami, Kerem Y. Camsari

雑誌: IEEE 68th International Annual Meeting on Electronic Devices

その他のニュース:

その他のトピック

「インターネット愛好家。ビール愛好家。誇り高きテレビの第一人者。邪悪な音楽の専門家。フレンドリーなベーコン ファン。微妙に魅力的なソーシャル メディア中毒者。ウェブ研究者」